Summary

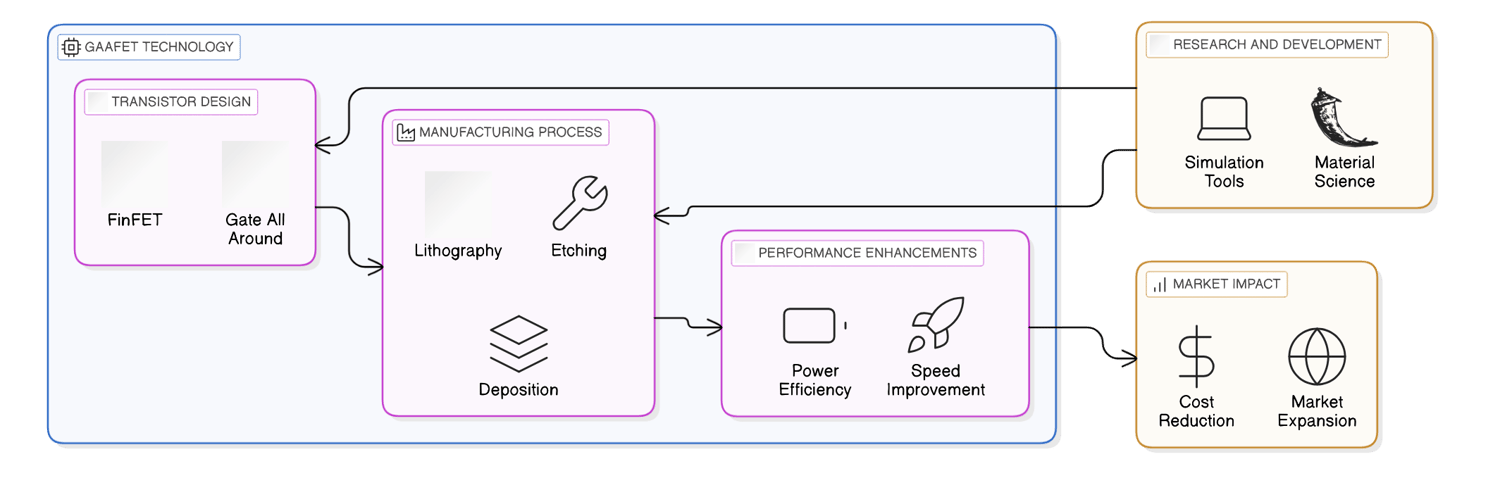

Bài viết này khám phá GAAFET - một bước đột phá trong sản xuất chip máy tính, đồng thời mang lại những giá trị quan trọng cho độc giả về tương lai của công nghệ bán dẫn. Key Points:

- GAAFET đang đối mặt với sự cạnh tranh khốc liệt từ các công nghệ như CFET và FET 2D, nơi chi phí sản xuất và hiệu suất sẽ quyết định ai là người dẫn đầu trong tương lai.

- Việc kiểm soát hiệu ứng ngắn kênh và biến đổi ngưỡng điện áp là thách thức lớn cho GAAFET, đòi hỏi nghiên cứu về vật liệu mới và kỹ thuật chế tạo tiên tiến.

- GAAFET không chỉ thay đổi cấu trúc transistor mà còn yêu cầu cải tiến quy trình thiết kế chip, điều này cần phát triển các công cụ EDA tối ưu hơn.

Giới thiệu về GAAFET và sự chuyển mình trong ngành sản xuất chip

FinFET là gì và tại sao cần depopulation

### **Tổng quan về FinFET và Depopulation**

Phương pháp chính để tăng mật độ transistor kể từ khi ra đời FinFET là giảm số lượng linh kiện (depopulation), thay vì chỉ đơn thuần thu nhỏ kích thước linh kiện như trước đây. Việc depopulation cho phép tích hợp nhiều transistor hơn vào cùng một không gian, đồng thời giảm thiểu độ nhiễu và nâng cao tốc độ xử lý, từ đó mang lại những lợi ích rõ rệt trong thiết kế mạch tích hợp. Điều này đặc biệt quan trọng với sự phát triển của công nghệ hiện đại, nơi mà yêu cầu về hiệu suất và tiết kiệm năng lượng ngày càng cao.

Ngoài ra, những vật liệu tiên tiến như graphene hay silic cacbua (SiC) đang được nghiên cứu để cải thiện thêm hiệu suất của các thành phần điện tử này. Những đổi mới trong cấu trúc FinFET đã mở ra hướng đi mới cho việc tối ưu hóa thiết kế chip máy tính, khẳng định vai trò then chốt của depopulation trong ngành công nghiệp bán dẫn hiện nay.

| Tiêu đề | Nội dung |

|---|---|

| GAAFET là gì? | Công nghệ transistor mới, cải tiến hiệu suất năng lượng và công suất so với FinFET. |

| Lợi ích của GAAFET | Cải thiện kiểm soát dòng điện, giảm rò rỉ điện năng, tiết kiệm năng lượng. |

| Đặc điểm chính | Sử dụng kênh nhiều dải để tối ưu hóa diện tích bề mặt giữa cổng và kênh. |

| Thách thức sản xuất | Quy trình sản xuất phức tạp hơn FinFET, yêu cầu vật liệu hi sinh mới. |

| Tương lai của chip máy tính | Dự kiến tích hợp cấu hình nhiều transistor trên mỗi fin vào năm 2028. |

Cách thức hoạt động của FinFET qua các hình ảnh

GAAFET là gì và điểm khác biệt với FinFET

Free Images

Free ImagesSự phát triển công nghệ từ FinFET đến GAAFET

Sau nhiều lần thử nghiệm quy trình sản xuất, công nghệ chế tạo FinFET hiện tại trung bình chỉ có khoảng hai fin cho mỗi transistor. Tuy nhiên, đến giai đoạn này, FinFET đã không còn khả năng tăng trưởng (hay giảm bớt) nữa. Để đạt được cấu trúc transistor với một fin duy nhất, cần có những cải tiến đáng kể về hình thái nhằm nâng cao hiệu suất năng lượng của từng fin. GAAFET chính là giải pháp cho những cải tiến hình thái đó.

GAAFET hứa hẹn mang lại nhiều lợi ích so với FinFET nhờ vào nguyên lý hoạt động mới giúp kiểm soát dòng điện hiệu quả hơn và giảm thiểu tình trạng rò rỉ điện năng. Việc sử dụng vật liệu tiên tiến như graphene hoặc các vật liệu 2D cũng sẽ giúp nâng cao hiệu suất và tiết kiệm năng lượng trong quá trình vận hành.

Hơn nữa, GAAFET có thể được ứng dụng trong nhiều thiết bị công nghệ hiện đại từ điện thoại thông minh đến máy chủ dữ liệu lớn, mở ra tiềm năng to lớn cho ngành sản xuất chip máy tính trong tương lai gần.

Tại sao việc chuyển đổi sang GAAFET lại mất nhiều thời gian?

Thách thức trong quy trình sản xuất GAAFET

Lợi ích của GAAFET đối với hiệu suất năng lượng

GAFEFt có ý nghĩa như thế nào cho tương lai công nghệ chip?

Tương lai sau GAAFET: CFET sẽ là gì?

Bạn có thể tự hỏi điều gì sẽ xảy ra tiếp theo? Bởi vì GAAFET thường sử dụng 1 fin cho mỗi transistor, liệu các thế hệ tương lai có phải quay lại việc thu nhỏ fins và gates để tăng mật độ không? Câu trả lời vẫn là không! Thay vào đó, các nhà sản xuất sẽ bắt đầu tích hợp cấu hình hỗ trợ nhiều hơn 1 transistor trên mỗi fin. Tôi sẽ thảo luận về tương lai xa vời này vào khoảng năm 2028 trở đi trong bài viết tiếp theo của mình về CFET.

Ngoài ra, cần nhấn mạnh rằng CFET hoạt động bằng cách sử dụng cả điện tử và lỗ trống nhằm nâng cao hiệu suất tổng thể. Việc áp dụng vật liệu mới như graphene hoặc các hợp chất hai chiều cũng rất quan trọng, bởi chúng có khả năng giảm tiêu thụ năng lượng và gia tăng tốc độ chuyển đổi trong vi mạch và thiết bị di động, từ đó làm nổi bật tầm quan trọng của CFET trong tương lai gần.

Reference Articles

Chip 5nm của IBM có thể tăng thời lượng pin gấp bốn lần

IBM tuyên bố rằng thiết kế GAAFET ấn tượng hơn so với FinFET sử dụng trong các chip hiện tại. Mặc dù FinFET có thể giảm xuống ở cấp độ 5nm nhưng ...

Bước đột phá ở quy mô nano của TSMC: 2nm và N4C ...

N4C dự kiến sẽ bắt đầu được sản xuất hàng loạt vào năm tới. Với kinh nghiệm phong phú và năng suất cao của TSMC trong quy trình 5nm, N4C được kỳ ...

Source: VnReviewTất tật về phần mềm thiết kế chip EDA, mặt trận ...

Những phần mềm bị hạn chế là các công cụ được sử dụng cho thiết kế chip kiến trúc GAAFET (gate-all-around field-effect transistor: bóng bán dẫn ...

Source: Báo MớiIntel Foundry sẵn sàng cho năm 2025 với tiến trình 18A và ...

Các công cụ này hỗ trợ khách hàng tận dụng toàn bộ tính năng của kiến trúc transistor RibbonFET gate-all-around (thiết kế với toàn bộ cổng bọc ...

Source: phamhongphuoc.netApple bắt đầu đầu tư vào nghiên cứu công nghệ 2nm của ...

Theo những nguồn tin được công bố, TSMC dự kiến sẽ bắt đầu sản xuất chip 2nm vào nửa cuối của năm 2025. Điều đáng chú ý ở đây là kích thước ...

Source: Minh Đạt StoreMặc dù chip 5nm vẫn chưa xuất hiện trên thị trường, TSMC ...

- Kế hoạch sản xuất chip 3nm và 2nm của TSMC với công nghệ FinFET mới GAAFET. - Việc sản xuất chip dưới 5nm sẽ khó khăn và đòi hỏi nguyên liệu đặc biệt.

Source: Mytour

ALL

ALL Quan hệ công chúng và tiếp thị

Quan hệ công chúng và tiếp thị

Related Discussions